| ENGENHARIA DE COMPUTAÇÃO                                                                                    |   |

|-------------------------------------------------------------------------------------------------------------|---|

| Gerson Miguel Beckenkamp                                                                                    |   |

| ARQUITETURA DE MÁQUINA DE PILHA, IMPLEMENTAÇÃO E AVALIAÇÃO<br>DE PROCESSADOR EM UMA DESCRIÇÃO DE ALTO NÍVEL | ) |

Santa Cruz do Sul, dezembro de 2015

## ENGENHARIA DE COMPUTAÇÃO

Gerson Miguel Beckenkamp

# ARQUITETURA DE MÁQUINA DE PILHA, IMPLEMENTAÇÃO E AVALIAÇÃO DE PROCESSADOR EM UMA DESCRIÇÃO DE ALTO NÍVEL

Prof. Eduardo Weber Wächter Orientador

Santa Cruz do Sul, dezembro de 2015

## ENGENHARIA DE COMPUTAÇÃO

Gerson Miguel Beckenkamp

# ARQUITETURA DE MÁQUINA DE PILHA, IMPLEMENTAÇÃO E AVALIAÇÃO DE PROCESSADOR EM UMA DESCRIÇÃO DE ALTO NÍVEL

Prof. Leandro Sehnem Heck Avaliador

## ENGENHARIA DE COMPUTAÇÃO

Gerson Miguel Beckenkamp

# ARQUITETURA DE MÁQUINA DE PILHA, IMPLEMENTAÇÃO E AVALIAÇÃO DE PROCESSADOR EM UMA DESCRIÇÃO DE ALTO NÍVEL

Prof. Guilherme Castilhos Avaliador

| Gerson Miguel Beckenkamp    |                                                                                                                                                                                                           |  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                             |                                                                                                                                                                                                           |  |  |  |

|                             |                                                                                                                                                                                                           |  |  |  |

|                             |                                                                                                                                                                                                           |  |  |  |

| ARQUITETURA DE MÁQUINA DE 1 | PILHA, IMPLEMENTAÇÃO E AVALIAÇÃO                                                                                                                                                                          |  |  |  |

| DE PROCESSADOR EM U         | MA DESCRIÇÃO DE ALTO NÍVEL                                                                                                                                                                                |  |  |  |

|                             |                                                                                                                                                                                                           |  |  |  |

|                             |                                                                                                                                                                                                           |  |  |  |

|                             | Trabalho de Conclusão II apresentado ao Curso de Engenharia da Computação da Universidade de Santa Cruz do Sul, como requisito parcial para a obtenção do título de Bacharel em Engenharia da Computação. |  |  |  |

|                             | Orientador: Prof. Eduardo Weber Wächter                                                                                                                                                                   |  |  |  |

|                             | Offeniador, From Eduardo Weber Wachter                                                                                                                                                                    |  |  |  |

|                             |                                                                                                                                                                                                           |  |  |  |

|                             |                                                                                                                                                                                                           |  |  |  |

#### **RESUMO**

Máquinas com arquitetura orientada a pilha são uma alternativa as arquiteturas de registradores encontradas nos computadores atuais. Em uma máquina de pilha, as instruções não precisam endereçar operandos pois o comportamento da pilha limita o acesso a uma posição referente ao topo da mesma, embora algumas abordagens permitam o endereçamento de até dois operandos. Esta abordagem pode apresentar algumas vantagens em relação a máquinas de registradores, visto que esta máquina trabalha naturalmente com pilhas para qualquer operação aritmética, lógica ou de chamada de função. Enquanto que em máquinas de registradores, estruturas de pilha precisam ser montadas e acessadas em memória, o que normalmente tem menor desempenho em relação ao uso de registradores. Por outro lado, a máquina de registradores apresenta maior flexibilidade em relação a máquinas de pilha sem operandos, visto que o endereçamento explícito de operandos não requer nenhum tipo de movimentação na estrutura de memória para que os operandos sejam alocados no topo de uma pilha. Entretanto, a programação de máquinas de pilha se diferencia muito da programação normalmente utilizada em máquinas de registradores, tornando-as incompatíveis entre si. Com isto, propõem-se um estudo sobre as máquinas de pilha de forma a analisar quais mudanças arquiteturais podem vir a apresentar maior impacto no desempenho do sistema. Ainda, espera-se obter uma comparação de desempenho com uma arquitetura baseada em registradores.

Palavras-chave: Máquina de pilha, máquina de registradores, arquitetura de computadores.

**ABSTRACT**

Machines with stack oriented architecture are an alternative to register architectures found

in today's computers. In a stack machine, the instructions do not need address operands because

the stack behavior limits the access to a position on the top of it, although some approaches

allow addressing of up to two operands. This approach may have some advantages over registers

machines, since this machine works naturally with stack for any arithmetic, logic or function

call. While in registers machines, stack structures need to be mounted and accessed in memory,

which typically has lower performance compared to using registers. On the other hand, the

register machine has greater flexibility compared to no operand stack machines, as the explicit

addressing operands does not require any drive in the memory structure so that the operands are

allocated on top of a stack. However, the stack machine programming is substantially different

from the typically programming used in registers machine, making them incompatible. With this,

we propose a study of the stack machines in order to analyze architectural changes which are

likely to have greater impact on system performance. Still, it is expected to obtain a performance

comparison with a register-based architecture.

**Keywords:** Stack machine, register machine, architecture.

# LISTA DE ILUSTRAÇÕES

| 1  | Exemplo do uso da pilha de dados em uma chamada de função                                      | 20 |

|----|------------------------------------------------------------------------------------------------|----|

| 2  | Exemplo do uso da pilha de retorno em uma chamada de função                                    | 21 |

| 3  | Esquema básico da VM Forth                                                                     | 23 |

| 4  | Conjunto de instruções para J1                                                                 | 29 |

| 5  | Diagrama de blocos da J1                                                                       | 30 |

| 6  | Conjunto de instruções específicos da ULA                                                      | 30 |

| 7  | Diagrama de bloco básico para o <i>MicroCore</i>                                               | 33 |

| 8  | Formato da instrução de 8 bits                                                                 | 33 |

| 9  | Diagrama de bloco do <i>Novix NC4016</i>                                                       | 36 |

| 10 | Conjunto de instruções do <i>Novix NC4016</i>                                                  | 37 |

| 11 | Manipulação dos <i>belts</i> ao chamar uma função                                              | 40 |

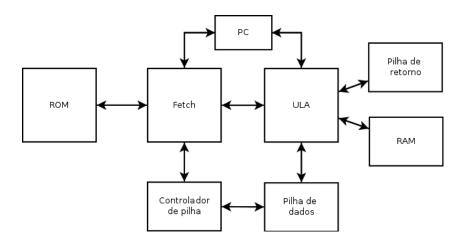

| 12 | Visualização de uma iteração entre as pilha de dados e retorno com a ULA e o registrador de PC | 44 |

| 13 | Visualização de uma escrita de endereço no registrador de PC                                   | 45 |

| 14 | Diagrama de blocos da máquina de zero operandos                                                    | 54 |

|----|----------------------------------------------------------------------------------------------------|----|

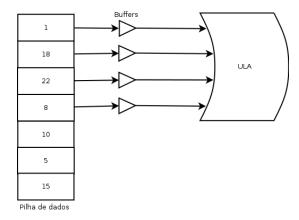

| 15 | Ilustração do acesso ao topo da pilha de dados por meio de <i>buffers</i>                          | 55 |

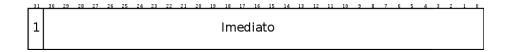

| 16 | Formato de instrução para instanciação de imediatos                                                | 56 |

| 17 | Formato de instrução para operações de desvio                                                      | 57 |

| 18 | Formato de instrução para acesso à memória RAM                                                     | 57 |

| 19 | Formato de instrução para operações de ULA                                                         | 58 |

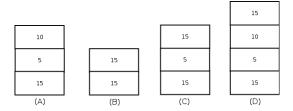

| 20 | Exemplo de diferentes modulações de pilha                                                          | 60 |

| 21 | Diagrama de blocos da máquina de dois operandos                                                    | 62 |

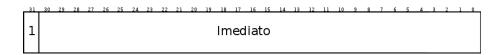

| 22 | Formato de instrução para instanciação de imediatos                                                | 64 |

| 23 | Formato de instrução para operações de desvio                                                      | 65 |

| 24 | Formato de instrução para acesso à memória RAM                                                     | 66 |

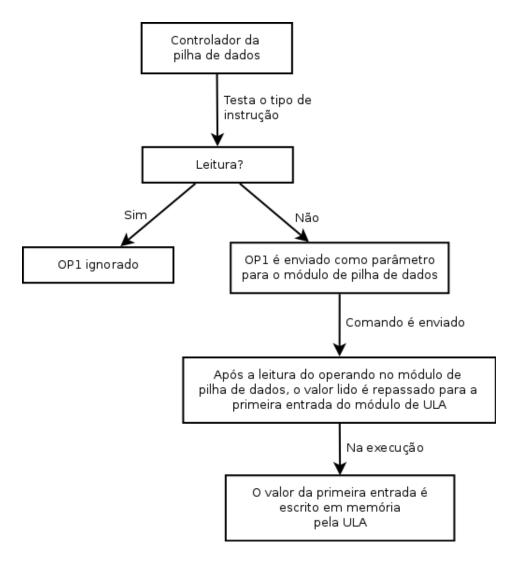

| 25 | Fluxograma da tomada de decisões no módulo controlador de pilha referente ao primeiro operando     | 67 |

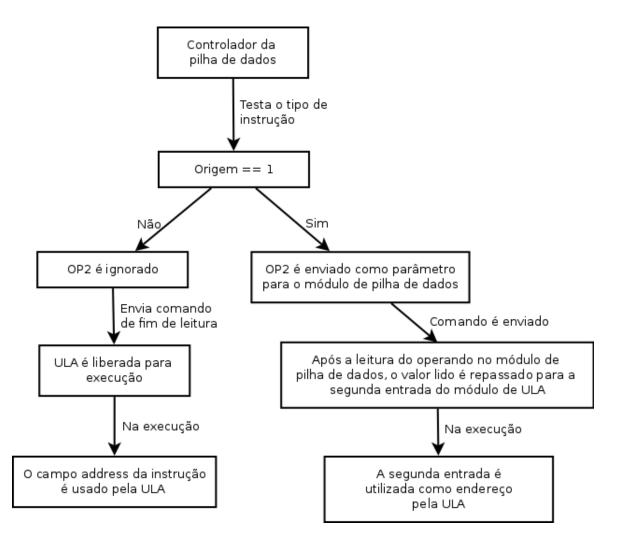

| 26 | Fluxograma da tomada de decisões no módulo controlador de pilha referente ao segundo operando      | 68 |

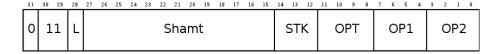

| 27 | Formato de instrução para operações de ULA                                                         | 69 |

| 28 | Exemplo de instrução para operações de adição de operados e adição com <i>offset</i>               | 71 |

| 29 | Comportamento da pilha de dados da 20p com a comparação das primeiras posições do vetor em memória | 79 |

| 30 | Comportamento da pilha de dados da 00p com a comparação das primeiras posições      |    |

|----|-------------------------------------------------------------------------------------|----|

|    | do vetor em memória                                                                 | 80 |

| 31 | Comportamento da pilha de dados na troca de valores em memória                      | 81 |

| 32 | 2 Efeito da chamada e retorno de função sobre a máquina                             | 82 |

| 33 | 3 Endereçamento dos registradores temporais                                         | 83 |

| 34 | 4 Testes realizados sobre a pilha de dados $0op$                                    | 85 |

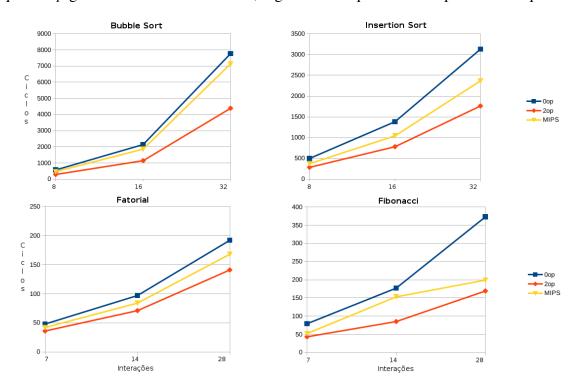

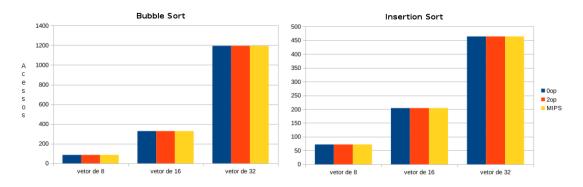

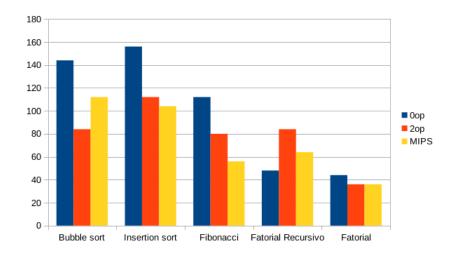

| 35 | 5 Resultados do total de ciclos de execução para todos os algoritmos                | 87 |

| 36 | 6 Resultados do total de acessos à memória para todos os algoritmos                 | 88 |

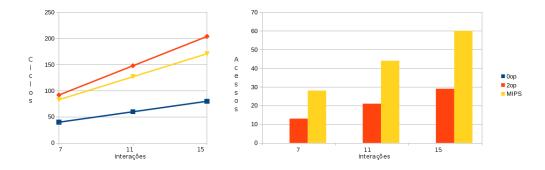

| 37 | Resultados obtidos com o algoritmo recursivo. O gráfico da esquerda informa o total |    |

|    | de ciclos de execução e o gráfico da direita informa o total de acessos à memória   | 88 |

| 38 | Tamanho de programa para cada um dos algoritmos em <i>bytes</i>                     | 90 |

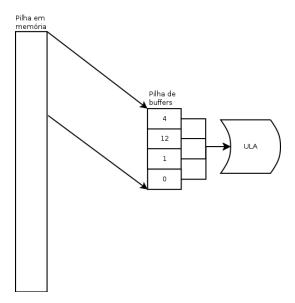

| 39 | Pilha de <i>buffers</i> sincronizada com a pilha alocada em memória                 | 95 |

#### LISTA DE TABELAS

| 1  | Diferença de tamanho entre os códigos das duas versões da aplicação                    | 32 |

|----|----------------------------------------------------------------------------------------|----|

| 2  | Opcodes para o campo de tipo                                                           | 34 |

| 3  | Opcodes para o campo de pilha                                                          | 34 |

| 4  | Opcodes para o campo grupo e as instruções geradas a partir dos campos tipo e pilha    | 34 |

| 5  | Opcodes de controle da ULA                                                             | 37 |

| 6  | Entradas secundarias para ULA                                                          | 38 |

| 7  | Opcodes para deslocamento                                                              | 38 |

| 8  | Tabela comparativa entre as máquinas analisadas nesta capitulo                         | 42 |

| 9  | Comparação entre número de pilhas                                                      | 47 |

| 10 | Relação de instruções primitivas <i>Forth</i> que acessam elementos profundos na pilha | 48 |

| 11 | Operações encontradas nos campos SRC e DST                                             | 59 |

| 12 | Operações encontradas no campo MOD                                                     | 59 |

| 13 | Operações encontradas no campo CMD                                                     | 61 |

| 14 | Relação de operações do campo <i>OP</i> da instrução de desvio     | 66 |

|----|--------------------------------------------------------------------|----|

| 15 | Composição de operações encontradas no campo <i>OPT</i>            | 70 |

| 16 | Composição das operações do campo <i>STK</i>                       | 71 |

| 17 | Comparação das características das máquinas desenvolvidas e o MIPS | 72 |

| 18 | Operações básicas implementadas para o assembler da máquina 0op    | 75 |

| 19 | Operações básicas implementadas para o assembler da máquina 20p    | 76 |

#### LISTA DE ABREVIATURAS

ASIC Application Specific Integrated Circuit

CPU Central Process Unit

DS Data stack

DSP Digital Signal Processor

LIFO Last In First Out

MIPS Millions of Instructions Per Second

NTos Next to the top of the stack

PC Program Counter

RAM Random Acess Memory

RISC Reduced Instruction Set Computers

RS Return stack

TLM Transaction-Level Modeling

Tors Top of the Return Stack

Tos Top of the stack

ULA Unidade Lógica e Aritmética

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VM Virtual Machine

# SUMÁRIO

| 1 INTRODUÇÃO                                               | 12 |

|------------------------------------------------------------|----|

| 2 FUNDAMENTAÇÃO TEÓRICA                                    | 14 |

| 2.1 Máquina de registradores                               | 14 |

| 2.1.1 MIPS                                                 | 14 |

| 2.2 Máquina de pilha                                       | 16 |

| 2.2.1 Taxonomia de <i>hardware</i> em uma máquina de pilha | 16 |

| 2.2.2 A pilha de dados                                     | 19 |

| 2.2.3 A pilha de retorno                                   | 20 |

| 2.2.4 Chamadas de função                                   | 20 |

| 2.3 A linguagem Forth                                      | 21 |

| 2.4 Formas de codificação                                  | 24 |

| 2.4.1 Microcoded                                           | 24 |

| 2.4.2 Hardwired                                            | 24 |

| 2.5 SystemC                                                | 25 |

| 2.5.1 Modelagem em nível de transação (TLM)                | 25 |

| 3 REFERENCIAL BIBLIOGRÁFICO                                | 27 |

| 3.1 O microcontrolador J1                                  | 28 |

| 3.2 A máquina <i>Microcore</i>                             | 32 |

| 3.3 O microporcessador <i>Novix NC4016</i>                 | 35 |

| 3.4 A CPU <i>Mill</i>                                      | 39 |

| 3.5 Súmula                                                 |    |

| 4 ANÁLISE TEÓRICA SOBRE AS MÁQUINAS DE PILHA         | 43 |

|------------------------------------------------------|----|

| 4.1 Quantidade de pilhas                             | 43 |

| 4.1.1 Máquina de duas pilhas                         | 43 |

| 4.1.2 Máquina de duas pilhas vs máquina de uma pilha | 44 |

| 4.1.3 Máquinas com múltiplas pilhas                  | 45 |

| 4.2 Quantidade de operandos                          | 47 |

| 4.3 Tamanho de pilha                                 | 51 |

| 5 IMPLEMENTAÇÃO E FUNCIONAMENTO DAS MÁQUINAS         | 52 |

| 5.1 Visão geral                                      | 52 |

| 5.2 Máquina de zero operandos                        | 54 |

| 5.2.1 Conjunto de instruções                         | 56 |

| 5.3 Máquina de dois operandos                        | 62 |

| 5.3.1 Conjunto de instruções                         | 64 |

| 5.4 Súmula                                           | 72 |

| 6 VALIDAÇÃO E CASOS DE TESTE                         | 73 |

| 6.1 Assembler                                        | 73 |

| 6.2 Programação                                      | 77 |

| 6.2.1 Analise de algoritmo                           | 77 |

| 7 RESULTADOS                                         | 86 |

| 8 CONCLUSÃO                                          | 92 |

| 8.1 Considerações finais                             | 93 |

| 8.2 Trabalhos futuros                                | 94 |

| REFERÊNCIAS                                          | 96 |

### 1 INTRODUÇÃO

Arquiteturas de máquinas utilizando pilhas são uma alternativa as arquiteturas de computadores utilizadas atualmente, que utilizam registradores como forma de trabalhar com os operandos. Apesar de algumas implementações em ASIC terem sido fabricadas e comercializadas no passado, o presente desta tecnologia encontra-se esquecido tanto na indústria quanto na academia.

Máquinas de pilha apresentam características que podem vir a trazer maior desempenho em certos cenários, quando comparadas as máquinas de registradores, pois estas fazem uso de estruturas de pilhas em um nível de memória mais alto do que a usada em máquinas de pilha. Contudo, a programação orientada a pilha sendo mais complexa do que a programação orientada a registrador, pois boa parte das máquinas de pilha não permitem o endereçamento explicito de qualquer posição da pilha, mas somente o topo da pilha.

O desenvolvimento deste trabalho utiliza a linguagem de programação e descrição de *hard-ware SystemC*. Esta permite a descrição de *hardware* em um maior nível de abstração se comparado com VHDL e *Verilog*, por exemplo, o que possibilita um tempo de desenvolvimento reduzido. Para aumentar o grau de abstração, será utilizado Transaction Level Modeling(TLM), que lida com barramentos entre módulos de forma mais genérica e simples, atingindo assim um melhor aproveitamento do espaço de projeto.

Este volume é dividido da seguinte forma. O Capítulo 2 apresenta a teoria básica sobre os temas apresentados neste trabalho, como máquinas de pilha e registradores. O Capítulo 3 apresenta uma análise de algumas implementações já existentes de máquinas de pilha, bem como as otimizações encontradas nas máquinas analisadas. O Capítulo 4 apresenta uma analise detalhada

sobre as principais características de uma arquitetura de máquina de pilha, propondo otimizações e as vantagens e desvantagens destas.

O Capítulo 5 apresenta como as arquiteturas de máquina de pilha implementadas para este projeto foram desenvolvidas e como estas funcionam. No Capítulo 6 é explicado como foram implementados os algoritmos para as máquinas propostas, bem como as ferramentas desenvolvidas. O Capítulo 7 apresenta os resultados obtidos com as máquinas desenvolvidas, comparando-as entre si e com uma máquina de registradores. Por fim, o Capítulo 8 apresenta a conclusão sobre as máquinas implementadas e os resultados obtidos.

### 2 FUNDAMENTAÇÃO TEÓRICA

Neste capítulo são apresentados tópicos relacionados aos presente trabalho que se fazem necessários para o entendimento deste Trabalho de Conclusão.

#### 2.1 Máquina de registradores

Uma máquina de registradores consiste em uma arquitetura onde um conjunto de registradores formam a memória local da CPU, que é acessada de forma explicita pelos operandos na instrução. Com isto, a instrução deve especificar ambos os endereços de origem dos operandos, quanto o endereço de destino em relação ao banco de registradores. Este comportamento faz com que o processador tenha de buscar todos os operandos no banco de registradores a cada início de instrução e, ao término da execução, necessita que a posição de destino seja procurada novamente para a alocação do resultado.

#### **2.1.1** MIPS

MIPS é uma máquina de 32 *bits* desenvolvida na universidade de Stanford em 1981 (DA-VID A. PATTERSON, 2005). Tendo como abordagem manter o conjunto de instruções reduzido (RISC), contendo apenas seis tipos de instrução possíveis:

- Aritmética: responsável pelas operações matemáticas básicas;

- Transferência de dados: responsável por leitura e escrita na memória principal;

- Lógico: responsável por operações lógicas básicas;

- Deslocamento: responsável por deslocamentos dos bits de um operando;

- Desvio condicional: responsável por saltos a partir de igualdade ou não de dois operandos;

- Salto incondicional: responsável por saltos simples e saltos com retorno;

A maior parte do banco de registradores MIPS é utilizado para operações lógicas e aritméticas. Entretanto, alguns registradores são reservados para darem suporte a controle de estruturas de dados em memória principal e à passagem de parâmetros entre chamadas.

Em casos de chamadas de função, os registradores auxiliares entre \$a0 e \$a3 são utilizados para a passagem de parâmetros, os registradores \$v0 e \$v1 recebem o valor de retorno da função, e o registrador \$ra\$ guarda o endereço de retorno do contador de programa (PC) de retorno (DA-VID A. PATTERSON, 2005). Assim, estes registradores são utilizados exclusivamente para as tarefas citadas anteriormente, visto que caso sejam modificados de forma incorreta a execução da função não será correta e o resultado do processamento estará errado.

Entretanto, quando existe uma chamada de função durante a execução de uma função, é necessário o fazer uma cópia do valor de alguns registradores para a troca de contexto. Na arquitetura MIPS, por convenção, antes de uma chamada de função, o contexto é copiado para os registradores *s0* a *s7* (DAVID A. PATTERSON, 2005).

Para isto, os registradores de *frame pointer* (*\$fp*) e *stack pointer* (*\$sp*) são utilizados para gerenciar uma pilha na memória principal. A cada chamada de função, são passados à esta pilha os argumentos e retornos da chamada anterior que estavam alocados no banco de registradores. Desta forma, a nova chamada pode alocar seus argumentos, retorno e endereço de retorno diretamente no banco de registradores sem afetar o comportamento da chamada anterior. Quando a chamada corrente na CPU for terminada, a chamada anterior pode ser carregada de volta da memória principal.

Outro requisito necessário ao MIPS é dar suporte a variáveis estáticas, que são mantidas independente do início e término de funções e chamadas. Para isto o MIPS designa um registrador chamado *global poiter \$gp*, que é responsável por indexar a posição de memória em relação ao frame pointer onde as variáveis estáticas estão guardadas.

#### 2.2 Máquina de pilha

Uma pilha é uma estrutura de dados do tipo *Last In First Out* (LIFO) cuja a única interface de acesso é sua posição mais ao topo. Sua implementação é feita de forma que o menor endereço de memória fique sempre como o último valor alocado, fazendo com que a pilha cresça na direção do maior endereço de memória. Um ponteiro chamado *Top of stack* (Tos) é usado para guardar a posição de memória mais ao topo da pilha, permitindo assim que a posição de memória do topo da pilha não precise ser fisicamente apagada em caso de retirada de valor da pilha, visto que logicamente este valor não faz mais parte da mesma (PHILIP J. KOOPMAN, 1989).

Os comandos mais básicos de uma pilha são os de empilhamento (*push*) e desempilhamento (*pop*). Ao executar um comando de *push*, o valor a ser adicionado a pilha é carregado no endereço de memória acima de Tos e após a escrita do valor, Tos é atualizado com a nova posição de topo. Ao chamar um *pop*, o valor contido no endereço de Tos será devolvido a quem fez a chamada e Tos será atualizado com o próximo endereço abaixo do topo da pilha anterior.

Desta forma, toda e qualquer operação lógica ou aritmética que envolva mais de um valor contido na pilha implica no consumo destes valores. Isto acontece pois a pilha pode apenas inserir ou expelir valores de seu topo, o que leva à retirada de um valor da estrutura de memória para que este possa ser computado.

#### 2.2.1 Taxonomia de hardware em uma máquina de pilha

É descrito por Philip Koopman como: "Uma taxonomia de *hardware* separa em grupos diferentes ramificações de um determinado tipo de máquina baseando-se em aspectos importantes na implementação da mesma. Uma boa taxonomia permite a observação de questões de design sem aprofundar-se nos detalhes de implementação de uma determinada máquina".

O espaço de planejamento de uma arquitetura em máquina de pilha é moldado em três aspectos principais, sendo elas o tamanho da pilha, quantidade de pilhas e o número de operandos na instrução. Cada um destes aspectos tem importância vital na forma como a máquina se comporta e em seu resultado final, permitindo-se assim implementar uma máquina mais adequada à uma determinada aplicação.

#### 2.2.1.1 Tamanho da pilha

O tamanho da pilha tem grande importância sobre o desempenho de uma máquina de pilha pois afeta diretamente a quantidade de iterações necessárias com a memória RAM. Segundo *Koopman*, uma pilha com mais de 16 posições de memória é considerada grande, embora esta noção de tamanho esteja muito mais ligada ao escopo do projeto do que a um tamanho prédefinido.

Por um lado, pilhas maiores podem comportar um maior número de valores em sua estrutura, o que acaba dando maior autonomia em relação a acessos a memória RAM para carregamento de mais elementos. Contudo, esta abordagem pode diminuir o desempenho em casos de execução multi tarefa, já que a cada troca de contexto toda a pilha tem que ser guardada em memória.

Em pilhas de tamanho pequeno, as principais vantagens são a simplicidade de implementação em *hardware* e a manipulação mais rápida de elementos perto da base da pilha. Entretanto o acesso à memória principal é mais frequente, visto que o tamanho reduzido implica em um maior número de leituras e escritas.

#### 2.2.1.2 Quantidade de pilhas

Normalmente, máquinas que contém apenas uma pilha tem sua implementação em *hard-ware* mais simples comparado com máquinas com múltiplas pilhas, pois a CPU só precisa controlar uma unidade de memória interna. Porém, todo dado tratado pela máquina, incluindo passagem de parâmetros e endereços de sub-rotina, é guardado em uma única pilha. Como diferentes tipos de dados ficam guardados na mesma estrutura de memória, a programação da máquina se torna mais complexa e um maior número de operações de ajuste para trazer os valores desejados ao topo da pilha é requerido em chamadas de sub-rotinas.

Já em máquinas com múltiplas pilhas, o fluxo de controle para dados pode ser dividido em várias pilhas separadas, tornando o sistema mais organizado. Dentre as implementações de máquinas com múltiplas pilhas, a abordagem mais adotada é uma pilha de dados (DS) em conjunto com uma pilha de retorno (RS). Entretanto outras pilhas podem ser adicionadas, como

por exemplo, pilha para variáveis locais e pilha de parâmetros.

Uma importante vantagem de se implementar uma máquina com múltiplas pilhas é a de poder acessar múltiplos valores em um único ciclo de relógio. Possibilitando assim, que mais de uma operação seja feita simultaneamente.

#### 2.2.1.3 Número de operandos na instrução

Em relação aos operandos, uma arquitetura de máquina de pilha pode apresentar de 2 a nenhum operando. A mudança do número de operandos na instrução de uma máquina de pilha dita como será feito o acesso à pilha de dados, variando o comportamento da CPU como consequência. Com isto, o sistema tende a aumentar ou diminuir a complexidade de *hardware* conforme determinada abordagem é utilizada.

Uma arquitetura com nenhum operando é considerada uma máquina pura. Sua instrução suporta comandos ou apenas um carregamento de valor literal por vez, tendendo a ter menor tamanho de instrução e a mais simples das abordagens. As operações aritméticas e lógicas normalmente são feitas através do acesso indireto ao topo da pilha de dados, acesso este concedido por um ou dois *buffers* que estão sempre sincronizados com o topo da pilha. Desta forma, os operandos estão sempre prontos para serem usados, permitindo assim que o processo de busca de instrução (*fetch*) seja executado em paralelo com a operação da ULA, o que acaba por eliminar a necessidade do uso de *pipeline* nos estagios de *fetch* e armazenamento de operandos (*store*) (PHILIP J. KOOPMAN, 1989). Outra vantagem desta abordagem é a de que como não há operandos na instrução, as instruções podem ter até 8 *bits* contendo apenas o comando da computação a ser realizada (BAILEY, 1996).

Em máquinas que consideram um operando na instrução, permite-se que qualquer posição da pilha seja acessada para efetuar uma computação, enquanto o outro operando a ser carregado continua sendo o do topo da pilha. Esta abordagem garante uma maior flexibilidade em relação à máquina pura, pois permite o acesso de uma posição da pilha de forma explícita. Além disto, as máquinas de um operando podem suportar instruções da máquina de zero operandos. Por exemplo, se a máquina tiver uma palavra de 16 *bits* para instruções com um operando e 8 *bits* para zero operandos, pode-se atribuir uma *flag* na instrução indicando o número de operandos e

por consequência o tamanho da mesma. Desta forma, a máquina de um operando pode emular operações de zero operandos.

Por fim, a máquina com instruções de dois operandos é a abordagem mais explícita de todas, pois permite que duas posições da pilha sejam acessadas pela instrução. É a abordagem mais flexível pois não requer um grande controle sobre o fluxo de dados da pilha, já que qualquer posição pode ser acessada. Entretanto a abordagem é mais custosa em relação a *hardware*, visto que ambos os operandos devem ser buscados a pilha.

#### 2.2.2 A pilha de dados

A pilha de dados é utilizada principalmente para armazenar valores lógicos e aritméticos, servindo tanto de fonte como de destino de valores para a ULA. Outra finalidade atribuída a ela é a passagem de parâmetros em chamadas de sub-rotina. Sua alocação pode ser feita tanto em um banco de registradores da CPU quanto em memória RAM, dependendo dos requisitos do projeto. Apesar de ter a mesma forma de um banco de registradores comum, sua utilização como pilha muda o comportamento do resto da CPU devido ao seu modo de acesso.

Sua implementação básica é feita com um *buffer* apontando para o topo da pilha, cuja a funcionalidade principal é facilitar o acesso da pilha, mantendo o valor do topo da pilha carregado para o uso da CPU, em especial para uma das entradas da ULA. Em máquinas que implementam apenas Tos, operação que requerem mais de um operando realizam um *pop*, onde o valor retirado da pilha é guardado em um barramento de dados. Como Tos está agora apontando para o segundo operador, a ULA carrega os valores contidos em Tos e no barramento de dados, atualizando o topo da pilha com o valor resultante (PHILIP J. KOOPMAN, 1989).

Algumas implementações podem apresentar o *buffer* próximo ao topo da pilha (Ntos). Nestes casos, NTos é conectado a segunda entrada da ULA e ao barramento de dados, facilitando o acesso do mesmo. Em máquinas com ambos Tos e Ntos, operações com dois operandos permitem que a ULA acesse simultaneamente os operandos. Após a leitura dos valores da pilha, esta recebe um *pop*, restando apenas à ULA sobrescrever Tos com o valor calculado.

#### 2.2.3 A pilha de retorno

A pilha de retorno é um conjunto de memória complementar à pilha de dados que como ela, pode ser implementada tanto em um banco de registradores da CPU quanto em memória RAM. Sua finalidade principal na máquina é guardar endereços de retorno para as chamadas de função, dando assim suporte de *hardware* a sub-rotinas. Sendo que sua implementação é idêntica à de uma pilha de dados que contém apenas um *buffer* apontando para seu topo, que neste casso recebe o nome de Tors (*Top of return stack*).

#### 2.2.4 Chamadas de função

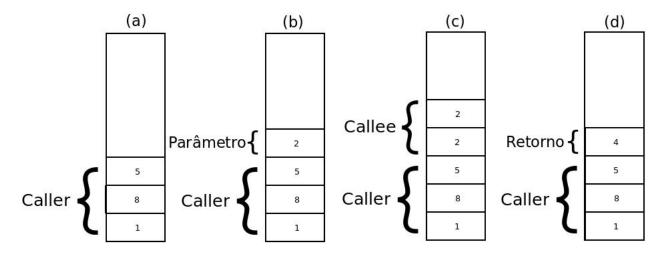

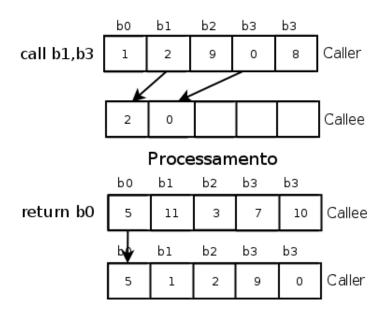

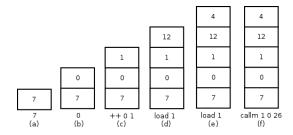

Antes de uma chamada de função, a função que invoca a chamada (*caller*) se responsabiliza por colocar os parâmetros mais ao topo da pilha de dados como visto na transição de *a* para *b* na Figura 1. Por convenção, a função invocada (*callee*) se responsabiliza por manipular a pilha somente a partir dos parâmetros, mantendo os dados do *caller* intactos como visto em *c*. Assim ao terminar sua execução, o *callee* deixa na pilha somente os valores de retorno e elimina da pilha todo o resto que tenha sobrado da computação *d*. Por fim, a função *caller* recebe a pilha de dados com sua partição de dados intacta e com os valores retornados da chamada mais ao topo.

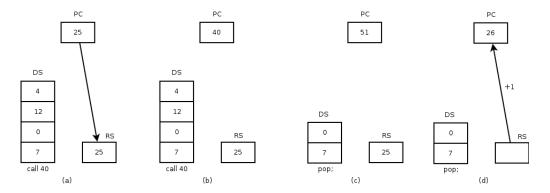

Figura 1: Exemplo do uso da pilha de dados em uma chamada de função.

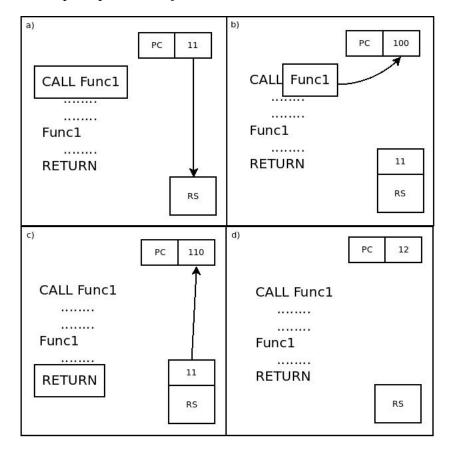

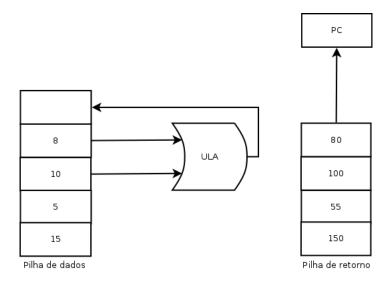

Como visto na Figura 2, ao executar uma chamada de função o PC é carregado na pilha de retorno a. Na sequência, o endereço onde o início do código da função está localizado é carregado no registrador de PC b. Após a execução da função, há uma chamada de retorno onde o último valor carregado na pilha re retorno é passado ao registrador de PC c, que na sequência

sofre um acréscimo d para que a execução continue.

Figura 2: Exemplo do uso da pilha de retorno em uma chamada de função.

#### 2.3 A linguagem Forth

Forth é uma linguagem de programação desenvolvida por Chuck Moore em meados dos anos 60, cuja sua primeira versão foi desenvolvida em ALGOL. De início, Forth era apenas um interpretador de textos que lê os comandos oriundos do teclado e executa funções baseadas neles (PELC, 2005). Posteriormente, a orientação à pilha foi adicionada na linguagem, devido a projetos de Moore em hardware orientado a pilha.

A linguagem *Forth* pode ser descrita como iterativa e extensiva. Iterativa porque pode funcionar em tempo real com entradas do teclado. Extensiva pois para *Forth* não há diferenciação entre funções nativas do sistema em relação as escritas pelo usuário. Aquilo que para outras linguagens de programação são chamadas funções, sub-rotinas e procedimentos, em *Forth* são chamadas de palavras. Todo e qualquer tipo de função, sub-rotina procedimento inserido pelo usuário é considerado da mesma forma pelo compilador, que após compilar, considera a palavra como nativa do sistema.

Para isto, *Forth* implementa um dicionário de palavras conhecidas pelo sistema. O dicionário vem carregado por padrão com todas as funções básicas da linguagem, como controle de laços, operações lógico e aritméticas, controle sobre memória, operações sobre pilha, etc. Conforme o usuário necessitar, mais palavras podem ser adicionadas a partir das primitivas básicas. Assim, o programador pode tanto programar chamadas em baixo nível diretamente com primitivas, quanto programar funções de alto nível com palavras preexistentes.

O pacote de execução em tempo real do *Forth* traz consigo um conjunto compacto de compilador, interpretador e ferramentas. Assim, o código *Forth* pode ser escrito tanto em terminal a partir do teclado quento carregado do disco, sendo que o código escrito em terminal pode ser salvo em disco. Isto permite que programas salvos anteriormente possam ser carregados por terminal ou acessados por outros programas.

Outra de suas características é a versatilidade de código entre alto e baixo nível de abstração. Uma aplicação pode ser escrita totalmente em alto nível de abstração sem precisar se preocupar com o código de máquina gerado. Após a validação da aplicação, palavras cuja a forma de funcionamento tenham que ser alteradas podem ser modificadas de forma individual em baixo nível de abstração (BRODIE, 2004).

Existem duas formas básicas de executar um programa em *Forth*, que são a execução em uma máquina de pilha física e o uso de máquinas virtuais. Considerando máquinas físicas, normalmente microcontroladores, o código é compilado e carregado diretamente na memória utilizada pela CPU. Com isto, podem ser tanto carregados códigos para alguma função específica quanto o compilador, o interpretador e as ferramentas *Forth*, possibilitando assim a utilização de um pequeno sistema operacional no microcontrolador.

Considerando a execução em máquina virtual(VM), o sistema executa sobre o sistema operacional corrente. Nesta VM o sistema operacional *Forth* sempre é carregado com a adição de funções especiais para possibilitar a comunicação de recursos com o sistema operacional hospedeiro (*host*), especialmente o acesso a arquivos.

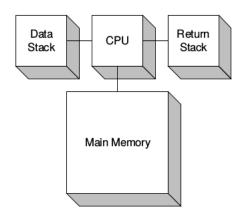

A VM *Forth* contém basicamente a CPU, a DS, a RS e a memória principal como visto na Figura 3. A CPU se conecta em paralelo com cada uma das memórias citadas, sendo as memórias para pilha de dados e retorno não endereçáveis e separadas da memória principal

(BRODIE, 2004).

Figura 3: Esquema básico da VM *Forth*. Fonte: (PELC, 2005).

Uma das peculiaridades da linguagem *Forth* é o uso de notação polonesa reversa (RPN). Sua adoção é dada pois esta notação tem como seu comportamento natural as operações em relação a pilha. Nesta notação, os valores a serem usados como operandos são carregados antes da chamada do operador, o que modulariza naturalmente o formato da expressão e elimina a necessidade de parenteses.

O Código 1 mostra um exemplo simples de definição de palavra em *Forth*. O compilador ira detectar uma palavra a partir do caractere ':' que define o início da palavra, e o caractere ';' que indica o fim da palavra. Após o início da palavra, o primeiro conjunto de caracteres nomeara a palavra, sendo este o nome a ser passado em código toda vez que a função for chamada. Na sequência, o '\*' indica a multiplicação dos dois componentes mais ao topo da pilha de dados, seguidos de um '.' que realiza desempilhamento do topo da pilha de dados para imprimir este valor no terminal.

Código 1: Trecho de código usado para definir uma palavra em *Forth*.

A segunda linha do Código 1 utiliza a nova palavra. Devido a noção RPN, os dois operandos são passados por primeiro ao compilador, que os interpreta como um empilhamento de valores na pilha de dados. Na sequência, o compilador chama a função referente à palavra especificada em código, que efetuara uma multiplicação entre os dois operandos ao topo da pilha

de dados. Com isto, o valor oito resultante da operação de multiplicação da linha anterior estará presente na pilha, que por fim é desempilhado para ser impresso no terminal.

#### 2.4 Formas de codificação

A maior parte dos processadores requer uma unidade de controle. Esta unidade de controle é responsável por decodificar as instruções e gerar os sinais de controle para um ou mais módulos da CPU. Na instrução, um ou mais grupos de *bits* são utilizados exclusivamente para informar à unidade de controle qual computação deve ser realizada. Com isto, esta instrução pode ser codificada basicamente de maneira *hardwired* e *microcoded*.

#### 2.4.1 Microcoded

É a maneira de codificação mais adotada nos processadores atuais. Consiste em uma memória rápida que se encontra na unidade de controle, e que pode ser programada com uma ou mais microinstruções de máquina. Com isto, o programador tem a liberdade de adicionar novas instruções informando ao processador o conjunto de microinstruções necessárias para a execução daquela função.

Este método garante maior flexibilidade na implementação da máquina pois as instruções aceitas pela máquina podem ser modificadas, permitindo assim que o sistema possa aceitar mais instruções ou que instruções antigas sejam alteradas. O método requer menor esforço do projetista visto que a instrução opera apenas na unidade de controle, sem ter efeito direto em nenhuma outra parte da CPU.

#### 2.4.2 Hardwired

Esta técnica de codificação foi a primeira a ser empregada em circuitos de controle. Ela permite que a instrução tenha acesso direto a qualquer módulo da CPU. Com isto, a unidade de controle necessita apenas selecionar, a partir da instrução, qual o sinal é endereçado a qual módulo.

Uma das principais vantagens desta abordagem é que a unidade de controle é bastante simples, necessitando de poucas portas lógicas para atribuir as funções de cada módulo da CPU, desta forma, acaba sendo mais rápido em relação a abordagem anterior (KOOPMAN, 1987). Por outro lado, esta abordagem requer que todas unidades funcionais da CPU já tenham seu comportamento definido para que a unidade de controle seja desenvolvida. Com isto, qualquer modificação na arquitetura requer que todo o controle da CPU seja redesenhado e alterado.

#### 2.5 SystemC

A linguagem *SystemC* tem como objetivo modelar circuitos de pequena a grande complexidade em nível de sistema. Garantindo maior flexibilidade no desenvolvimento de *hardware* e *software* em múltiplos níveis de abstração (SYSTEMC® REFERENCE MANUAL, 2012).

Trata-se de uma biblioteca para *C*++ com uma série de recursos para abstração de *hard-ware*, tipos de dados orientados a hardware, sincronização por meio de eventos e sensitividade, etc. Tornando assim possível que se descreva o comportamento de um circuito a partir de uma linguagem de programação de alto nível, se comparado a outras linguagens de descrição de *hard-ware*(HDL).

Recursos do *C*++ podem ser usadas no desenvolvimento da aplicação em conjunto com os recursos do *SystemC*. Porém, todos os recursos usados devem seguir as regras e restrições contidas no padrão *SystemC* (SYSTEMC® REFERENCE MANUAL, 2012).

Por permitir uma modelagem mais abstrata comparada a outras linguagens de descrição de *hardware*, o *SystemC* permite que sistemas de *hardware* de grande complexidade sejam avaliados com rapidez. Sendo assim, a validação de um sistema, bem como suas modificações, se tornam mais rápidas e fáceis, reduzindo o tempo de projeto.

#### 2.5.1 Modelagem em nível de transação (TLM)

*Transaction-level modeling* (TLM) consiste no uso de pacotes para abstrair a comunicação de barramentos entre módulos. Com isto, são utilizadas interfaces de transporte bloqueantes e não bloqueantes para transmitir pacotes de dados genéricos entre o módulo de origem e o módulo

de destino (SYSTEMC® REFERENCE MANUAL, 2012).

Para maximizar a interoperabilidade entre os *sockets*, o protocolo utilizado em cada comunicação pode ser personalizado. Isto junto da escolha de primitivas bloqueantes, conferem ao programador maior liberdade na elaboração da comunição entre módulos.

A utilização de TLM 2.0 em sistemas desenvolvidos em *SystemC* permite um grau mais elevado de abstração. Isto porque a criação de um barramento, bem como a implementação de seu protocolo, não é necessário. Ao invés disto, o TLM garante um canal de comunicação abstrato, configurável e com protocolo de recebimento de dados pré-estabelecido, facilitando a implementação e diminuindo o tempo de projeto.

#### 3 REFERENCIAL BIBLIOGRÁFICO

Neste capítulo são analisadas as máquinas utilizadas como referência no desenvolvimento do trabalho. Somente aspectos que cabem ao Trabalho de Conclusão serão detalhados, como formatos de instrução e tratamento de pilhas. Os demais tópicos como tratamento de interrupção e uso de *pipeline* não terão grande atenção porque este Trabalho de Conclusão não visa o uso destes recursos. Contudo, em uma futura continuidade do trabalho, estes tópicos podem se tornar interessantes.

Outro ponto a ser abordado em relação a análise dos conceitos referentes a este trabalho é a definição de uma máquina de pilha, uma máquina de registrador e uma máquina híbrida. Será considerado **máquina de pilha**, qualquer máquina cujo o banco de registradores seja tratado como pilha pelo sistema. Caso hajam *buffers* internos apontando à memória RAM, é considerado uma máquina de pilha somente se os blocos de memória apontados sejam tratados como pilha pelo processador, especialmente nos blocos utilizados para operações lógicas e aritméticas.

Uma **máquina de registradores** é aquela onde a memória local da máquina é acessada de forma totalmente explícita. Vale ressaltar que muitas arquiteturas deste tipo se utilizam de artifícios para garantir suporte em *hardware* a determinados recursos da RAM, especialmente para chamadas de função. Nestes casos é comum o uso de *buffers* em máquina para apontar estruturas de pilha em RAM. Mesmo assim, esta máquina continua a ser de registradores pois sua instruções de operação lógico e aritmética continuam sendo completamente explícita.

Por fim, uma **arquitetura híbrida** é aquela que fica entre os casos citados anteriormente. Tanto máquinas com uma pilha de dados e banco de registradores endereçáveis em CPU, quanto máquinas com pilhas auxiliares em *hardware* juntamente de um banco de registradores para

operações lógico aritméticas entram nesta categoria.

#### 3.1 O microcontrolador J1

A máquina *J1* foi criada com o intuito de ser um microcontrolador extremamente simples e eficiente para a transmissão de vídeo não compactado via *ethernet*. Para isso, a máquina implementa a maioria das microinstruções *Forth*, deixando de lado desvios relativos, interrupções, exceções, multiplicação e divisão.

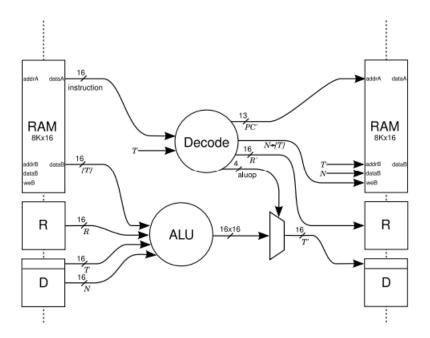

A J1 se apresenta como uma CPU de 16 bits, contendo uma pilha de dados de 33 posições (32 mais Tos), uma pilha de retorno de 32 posições e um contador de programa de 13 bits, sem nenhum outro tipo de memória interna para a alocação de estados. Além disto, buffers para as posições do topo da pilha (T) e próximo ao topo (N) são usados para acessar a pilha de dados, e outro buffer (R) é utilizado para acessar o topo da pilha de retorno. Como toda estrutura de memória manipulada pela máquina é somente de 16 bits, o uso de estruturas de dados que necessitam mais de 16 bits são implementadas em software.

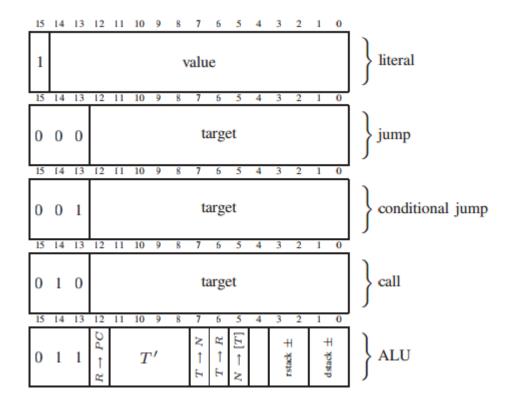

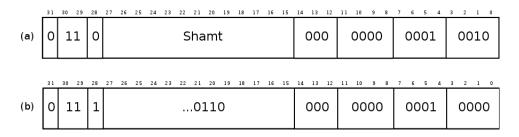

Uma das otimizações encontradas na J1 é o uso de instruções hardwired, isto é, a instrução ao invés de ser codificada é organizada em séries de bits que são atribuídos a determinada unidade funcional da CPU, que no caso da J1 são fetch e ULA. Com isso, a etapa de decodificação não é necessária já que todas as unidades funcionais já recebem suas tarefas diretamente da instrução. Como visto na Figura 4 estas instruções divididas entre literal, salto, salto condicional, chamada e ULA, como na maioria das demais máquinas de pilha.

Figura 4: Conjunto de instruções para J1. Fonte: (BOWMAN, 2010).

Em *Forth*, a instrução do tipo literal normalmente indica que a instrução a seguir é um valor a ser carregado e não uma instrução a ser executada, fazendo que a máquina gaste dois ciclos de relógio para carregar um valor na pilha. No caso da *J1*, o primeiro *bit* da instrução indica se a instrução é literal ou não, sendo o valor carregado dos demais 15 *bits* da instrução. No caso de carregamento de um valor que necessite do *bit* mais significativo, o compilador carrega os 15 *bits* do imediato com o valor invertido, e após executa uma instrução de inversão no topo da pilha. Desta forma, a máquina passa a carregar valores de até 15 *bits* em um ciclo de relógio.

Todos os endereços de chamada e salto são de 13 *bits*, limitando o tamanho do código para 16 KB. As principais otimizações encontradas neste tipo de instrução estão na ausência de salto relativo, o que impede a ocorrência de saltos para fora do limite de código pelo compilador. Outra otimização é encontrada na instrução nativa do *Forth* chamada *branch0*, onde em um único ciclo a máquina executa um *pop* no topo da pilha de dados e caso este seja igual a zero, passa o valor contido nos 13 *bits* para o PC.

Figura 5: Diagrama de blocos da J1. Fonte: (BOWMAN, 2010).

O tipo de instrução ULA é feita de forma que a execução da ULA não dependa de nenhum outro campo da instrução, tornando possível que esta unidade execute em paralelo com as demais unidades de *fetch* e decodificação, demonstrado no diagrama de blocos da Figura 5. Nesta instrução, várias unidades funcionais da ULA podem ser atribuídas a uma única chamada, especialmente em casos de retorno de função, onde o valor contido no topo da pilha de retorno pode ser passado diretamente ao PC ao final da execução desta instrução e tornando assim o retorno de função gratuito, ou seja, não requer mais um ciclo só para a chamada de retorno.

| code | operation   |  |  |

|------|-------------|--|--|

| 0    | T           |  |  |

| 1    | N           |  |  |

| 2    | T + N       |  |  |

| 3    | Tand $N$    |  |  |

| 4    | Tor $N$     |  |  |

| 5    | Txor $N$    |  |  |

| 6    | $\sim T$    |  |  |

| 7    | N = T       |  |  |

| 8    | N < T       |  |  |

| 9    | Nrshift $T$ |  |  |

| 10   | T-1         |  |  |

| 11   | R           |  |  |

| 12   | [T]         |  |  |

| 13   | Nlshift $T$ |  |  |

| 14   | depth       |  |  |

| 15   | Nu< $T$     |  |  |

|      |             |  |  |

Figura 6: Conjunto de instruções específicos da ULA. Fonte: (BOWMAN, 2010).

Com a junção dos campos da ULA mostrados na Figura 4 e do microcódigo apresentado na figura 6, é possível realizar um vasto número de instruções distintas de aritmética e de dados entre pilhas. Na terminologia mostrada em ambas T, N e R representam Tos, NTos e topo da pilha de retorno. Ao computar um comando da ULA, os campos dstack e rstack, vistos na instrução de ULA da Figura 4, são tomados como referência para o consumo (push ou pop) de determinada pilha. Desta forma, o comando referente aos campos de consumo serão aplicados antes do valor computado ser alocado no Tos, o que torna desnecessário o uso de buffers para a manipulação de valores na pilha de dados.

Na verdade, todos os campos da ULA mostrados na Figura 4 são efetuados antes da alocação do valor computado, caso haja algo a ser computado. A chamada do *opcode* da ULA pode também ser apenas um carregamento de um dos topos das pilhas, pois este é o único campo desta instrução que permite acessar este recurso para ser usado pelos demais campos, como um carregamento em memória por exemplo. Entretanto, uma atenção especial é necessária ao carregar o código 12 ou [T], vistos na Figura 6, pois este é exclusivamente referido à Tos e é interpretado como endereço de memória. Sendo assim, ao ser carregado, a máquina usa a variável carregada de Tos para buscar o valor desejado na RAM e aloca o valor encontrado em Tos, reescrevendo-a e realizando assim uma leitura em memória. A operação oposta pode ser obtida ativando o campo de *bit* 5 da instrução, sabendo-se que o valor a ser alocado deve estar em NTos e o endereço em Tos.

Além dos códigos de ULA citados anteriormente, existe um código que normalmente não é encontrado em aritméticas de outros processadores, seja de pilha ou de registrador, sendo este o de código 10, visto na Figura 6. Este, na verdade, é uma otimização natural para uma máquina de pilha pois todos os cálculos de endereços ou *index* são feitos na pilha de dados, Sendo assim, em casos onde vetores estão sendo tratados em RAM, o endereço referente ao vetor normalmente sofre adição ou subtração de uma posição por vez. O que requer que a máquina carregue um literal que após a soma será consumido e não poderá ser utilizado novamente em outro cálculo do mesmo tipo. Assim, adição desta instrução na ULA a máquina poupa 1 ciclo de relógio em cada cálculo de endereço, além de reduzir a quantidade de instruções de imediato no código, acarretando em melhor densidade de código.

Ao contrário de boa parte das CPUs que executam Forth apresentadas pela comunidade,

a J1 não é somente uma máquina conceitual para os conceitos herdados de uma determinada máquina de pilha ou com algum tipo de otimização criada pelo autor. A J1 vai além disto, sendo pensada para uma aplicação real e em consequência é possível quantificar seu desempenho, tornando possível a comparação com máquinas equivalentes existentes no mercado e a avaliação de benchmarks.

Quando comparado à versão anterior do sistema, onde mesma função era exercida por um microcontrolador *MicroBlaze* executando *C*, a *J1* otimizou em 62% o tamanho de código, permitindo que sejam adicionadas mais funcionalidades à aplicação. Apesar de não implementar *Forth* por completo, a *J1* consegue alcançar uma boa performance entregando 100 MIPS a 80 MHz, rodando em uma *Spartan 3E FPGA* (BOWMAN, 2010).

Na tabela 1 é mostrada a diferença de tamanho de código em relação a implementação anterior na *Microblaze*, na atual *J1* e na tentativa de construir o mesmo sistema em *Forth* na *Microblaze*. Apesar de não ser uma máquina de propósito geral, a *J1* consegue executar a aplicação para qual foi desenvolvida 3X a performance da plataforma baseada em *C* (BOWMAN, 2010).

Tabela 1: Diferença de tamanho entre os códigos das duas versões da aplicação.

| Component      | Code size (bytes) |      |           |

|----------------|-------------------|------|-----------|

|                | MicroBlaze        | J1   | MicroCore |

| $CI^2$         | 948               | 132  | 113       |

| SPI            | 180               | 104  | 105       |

| flash          | 948               | 316  | 370       |

| ARP responder  | 500               | 112  | -         |

| entire program | 16380             | 6349 |           |

Fonte: (BOWMAN, 2010).

#### 3.2 A máquina Microcore

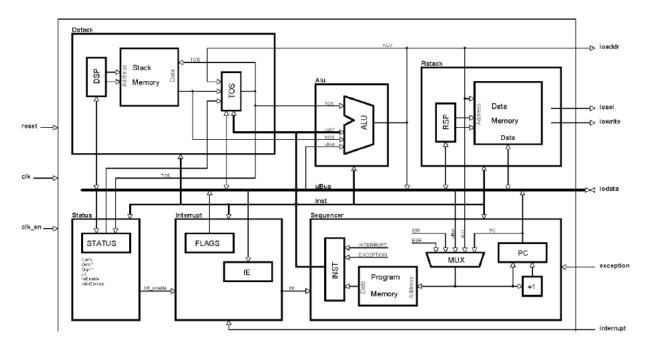

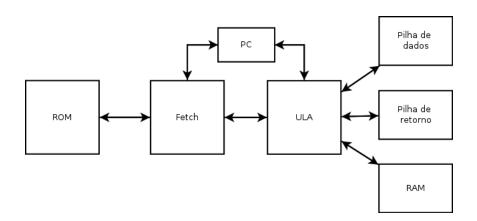

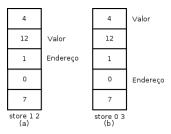

*Microcore* é uma máquina de duas pilhas, com arquitetura *harvard* primariamente desenvolvida para executar as primitivas *Forth* com instruções de 8 *bits*. Ambas pilha de dados e pilha de retorno são alocadas na RAM e podem ser acessadas separadamente, contando ainda com uma memória de programa ROM. Como mostrado na Figura 7, a arquitetura básica da máquina contém os módulos de pilha de dados, ULA, pilha de retorno, caminho de dados central (*uBus*) e Tos, sendo que mais funções podem ser adicionadas ao sistema conforme a necessidade do projeto.

Figura 7: Diagrama de bloco básico para o *MicroCore*. Fonte: (SCHLEISIEK, 2005).

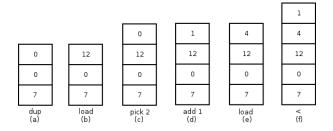

Como visto na Figura 8, a chamada de literal é dada com o *bit* mais significativo da instrução em 1, sendo os demais *bits* o valor a ser atribuído ao literal. Para variáveis maiores do que 7 *bits*, o compilador utiliza uma série de literais. Desta forma, a CPU reconhece a sequência de literais e começa a montar o topo da pilha de dados lendo cada literal e efetuando um deslocamento à esquerda para que a concatenação possa ser efetivada (SCHLEISIEK, 2004). Caso o primeiro *bit* da instrução não seja 1, a instrução passa a ser *opcode*, contendo na sequência 2 *bits* de tipo, 2 de pilha e 3 de grupo como mostrado na figura.

| 7      | 6 | 5   | 4 | 3     | 2 | 1    | 0  |  |

|--------|---|-----|---|-------|---|------|----|--|

| Lit/OP | Т | ipo | F | Pilha |   | Grup | 00 |  |

Figura 8: Formato da instrução de 8 *bits*. Fonte: Modificada pelo Autor (SCHLEISIEK, 2004).

No caso de um desvio, a CPU deve desempilhar o topo da pilha de dados para alocar o endereço de PC. Ao executar uma chamada de função, o PC é carregado para a pilha de retorno enquanto o novo endereço estiver sendo carregado e, após a execução da chamada, a instrução de retorno é responsável por carregar o topo da pilha de retorno para o PC. Como visto na Tabela 2, instruções do tipo ULA realizam operações aritméticas utilizando a pilha de dados como fonte e destino, MEM da acesso à RAM e USR, microcódigo cuja a funcionalidade pode ser programada pelo usuário, pode ser implementada conforme a aplicação necessitar.

Tabela 2: Opcodes para o campo de tipo.

| Código | Nome | Ação                                                            |

|--------|------|-----------------------------------------------------------------|

| 00     | BRA  | Desvio, chamada de função e retorno                             |

| 01     | ALU  | Operações unárias ou binárias                                   |

| 10     | MEM  | Acesso a memória e registrador                                  |

| 11     | USR  | Não usado pelo MicroCore, podendo ser implementado pelo usuário |

Fonte: (SCHLEISIEK, 2004).

Na Tabela 3 são mostrados os *opcodes* do campo de pilha, onde estão contidos os comandos básicos de *pop* e *push*, sendo os demais campos dependentes do campo tipo mostrados na Tabela 2 e de sinais externos, tornando o *opcode* não ortogonal e complexo. Os demais níveis de complexidade são apresentados pelo campo de grupo apresentado na Figura 8, que quando combinados com os demais campos do *opcode* podem gerar as primitivas *Forth* como mostrado na tabela 4. Como visto, o comportamento de uma determinada instrução depende dos três campos, o que permite que três diferentes módulos diferentes da máquina sejam chamados ao mesmo tempo no momento da execução.

Tabela 3: *Opcodes* para o campo de pilha.

| Código | Nome | Ação                                      |  |  |  |  |  |  |  |

|--------|------|-------------------------------------------|--|--|--|--|--|--|--|

| 00     | NONE | Não depende de tipo                       |  |  |  |  |  |  |  |

| 01     | POP  | $pilhas \rightarrow NTos \rightarrow Tos$ |  |  |  |  |  |  |  |

| 10     | PUSH | $Tos \rightarrow NTos \rightarrow pilhas$ |  |  |  |  |  |  |  |

| 11     | BOTH | Dependente de tipo                        |  |  |  |  |  |  |  |

Fonte: (SCHLEISIEK, 2004).

Tabela 4: *Opcodes* para o campo grupo e as instruções geradas a partir dos campos tipo e pilha.

| C- 1- | Binary-Ops | Unary-Ops | Complex-Math | Conditions | Branches | Registers |

|-------|------------|-----------|--------------|------------|----------|-----------|

| Code  | ALU        | ALU BOTH  | ALU NONE     | BRA        | BRA PUSH | MEM       |

| 000   | ADD        | NOT       | MULTS        | NEVER      | DUP      | STATUS    |

| 001   | ADC        | SL        | 0DIVS        | ALWAYS     | EXC      | TOR       |

| 010   | SUB        | ASR       | UDIVS        | ZERO       | QDUP     | RSTACK    |

| 011   | SSUB       | LSR       | not used     | NZERO      | QOVL     | LOCAL     |

| 100   | AND        | ROR       | LDIVS        | SIGN       | INT      | RSP       |

| 101   | OR         | ROL       | not used     | NSIGN      | IRET     | DSP       |

| 110   | XOR        | ZEQU      | not used     | NOVL       | THREAD   | TASK      |

| 111   | NOS        | CC        | SWAPS        | NCARRY     | TOKEN    | IP        |

Fonte: (SCHLEISIEK, 2004).

Um dos principais aspectos do MicroCore é se aproveitar da implementação em HDL para

gerar uma máquina customizada com as exigências da aplicação que será executada na FPGA, podendo gerar desde uma máquina simplista com poucas funcionalidades até uma máquina de pilha com suporte completo a *Forth*. Apesar disto, não foi encontrado nenhum tipo de aplicação real que se utilize desta máquina. É comentado em (SCHLEISIEK, 2005) sobre um protótipo de compilador que permitiria executar código *C* no *MicroCore*, porém este não encontra-se disponível ou tem qualquer tipo de demonstrações ou resultados apresentados.

# 3.3 O microporcessador *Novix NC4016*

O *NC4016* foi o primeiro microprocessador *Forth* 16 *bits* a ser fabricado, rodando a 8 MHz e usando cerca de 4000 portas lógicas em tecnologia 3 µm HCMOS. Tinha como objetivo executar aplicações de tempo em tempo real e alta velocidade na execução de *Forth* para programação de propósito geral (PHILIP J. KOOPMAN, 1989). Seu projeto original foi desenvolvido como um protótipo para validar a utilização de *Forh* em uma máquina de pilha física, porém acabou sendo comercializado tendo como foco o mercado de controle embarcado.

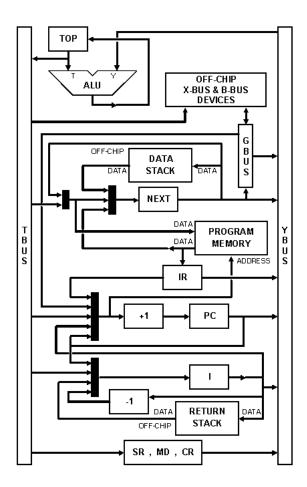

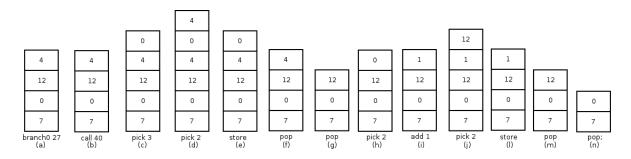

Como a tecnologia da época não permitia portar memórias locais ao *chip*, o *NC4016* utiliza dois canais de memória 16 *bits* para acessar as pilhas de forma externa e dedicada. Além dos canais utilizados para comunicar a pilha de dados e pilha de retorno, um canal é utilizado para acessar a RAM. Com isto, dois caminhos de dados são utilizados dentro do microprocessador como visto na figura 9, sendo um deles a interface com as duas pilhas e o outro a interface com a RAM. Este arranjo permite com que as pilhas sejam acessadas paralelamente com a RAM e assim facilita a execução monociclo para determinadas instruções.

Ambas as memórias externas para as pilhas têm 256 posições, sendo referenciadas pelos *buffers* Tos e NTos no caso da pilha de dados e Tors no caso da pilha de retorno presentes dentro do *chip*. Assim os *buffers* só precisam ser atualizados quando há alguma alteração na pilha à qual eles referenciam, o que otimiza o tempo de acesso ao recurso se comparado a um carregamento direto da memória externa. Porém, a utilização de memórias externas faz com que a CPU não tenha controle sobre sobrecarga de dados das pilhas.

Para aplicações com múltiplos processos, uma memória maior que 256 registradores pode ser utilizada. Com isto, cada processo pode mapear através das portas entrada e saída (E/S)

Figura 9: Diagrama de bloco do *Novix NC4016*. Fonte: (PHILIP J. KOOPMAN, 1989).

uma determinada área da memória externa para usar como pilha, limitando os *buffers* internos somente a estas áreas. Assim, as pilhas estão sempre carregadas e a troca de contexto só precisa fazer os *buffers* apontarem para a pilha referente ao próximo processo a ser executado, reduzindo o *overhead*.

O NC4016 tem 2 duas portas de E/S, sendo uma porta B com 16 bits de barramento, e outra X de 5 bits. Estas portas permitem que dispositivos externos tenham acesso ao microprocessador sem interromper outros barramentos de memória, e também podem ser usadas para estender o endereço de memória como citado anteriormente. Por padrão a máquina opera com tamanhos fixos de memória de 16 bits, fazendo assim com que o uso de estruturas de dados com tamanho diferente de 16 bits tenham que ser implementados em software.

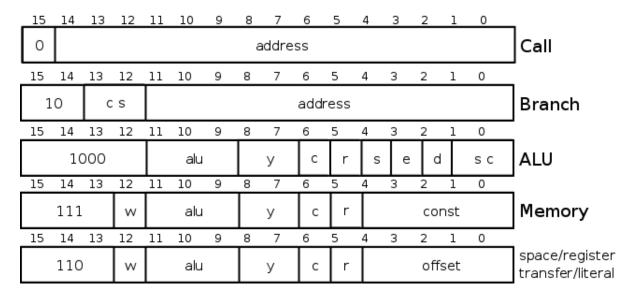

Quanto ao conjunto de instruções, o *NC4016* é o pioneiro no uso de instruções não codificadas, característica esta que foi herdada pela máquina *J1*, vista na Seção 3.1, e por muitas outras máquinas de pilha sucessoras a *NC4016*. Como visto na Figura 10 há cinco tipos de instrução,

onde por padrão o primeiro *bit* mais significativo indica uma chamada de função e os demais *bits* são interpretados como endereço caso seja chamado. No caso de um desvio, o campo *cs* é responsável por indicar a máquina se a chamada incondicional (*cs*=10), um laço referente ao registrador de índice (*cs*=11) ou ainda se o salto é condicional ao Tos ser igual a zero (*cs*=01).

Figura 10: Conjunto de instruções do *Novix NC4016*.

Nas demais instruções, não descritas na Figura 10, uma série de bits de controle se repete:

- w, controla a leitura ou escrita de memória;

- ULA, controla a ação da ULA caso haja uma operação unária ou binária, ou se responsabiliza por carregar o valor certo para ser usado pelos demais campos da instrução, descritos na Tabela 5.

Tabela 5: Opcodes de controle da ULA

| 000 | carrega Tos |

|-----|-------------|

| 001 | Tos and y   |

| 010 | Tos - y     |

| 011 | Tos or y    |

| 100 | Tos + y     |

| 101 | Tos xor y   |

| 110 | y - Tos     |

| 111 | у           |

Fonte: (PHILIP J. KOOPMAN, 1989).

• y, controla a segunda entrada da ULA conforme visto na Tabela 6.

Tabela 6: Entradas secundarias para ULA

| 00 | NTos                |

|----|---------------------|

| 01 | NTos com carry flag |

| 10 | registrador MD      |

| 11 | registrador SR      |

Fonte: (PHILIP J. KOOPMAN, 1989).

- c, copia o valor em Tos para NTos;

- r, retorno de subrotina (Tors  $\rightarrow PC$ );

- s, atua juntamente com o campo c para executar push ou pop na pilha de dados;

- *e*, habilita o deslocamento de 32 *bits*;

- sc, controla o comportamento do deslocamento executado pela ULA, visto na Tabela 7:

Tabela 7: *Opcodes* para deslocamento

| 00 | não efetua o deslocamento         |

|----|-----------------------------------|

| 01 | Deslocamento lógico à direita     |

| 10 | Deslocamento a esquerda           |

| 11 | Deslocamento aritmético à direita |

Fonte: (PHILIP J. KOOPMAN, 1989).

Instruções de memória demoram dois ciclos de relógio, um ciclo para a busca da instrução e outro para a operação (PHILIP J. KOOPMAN, 1989). O campo ULA neste caso pode realizar cálculos diretamente no endereço a ser utilizado a partir do campo de constante, visto que o endereço nestes casos sempre é pego em Tos. Este comportamento permite que cálculos de endereços não necessitem ser executados na pilha de dados, o que otimiza sua utilização e economiza alguns ciclos de relógio.

A última instrução mostrada na Figura 10 pode ser considerada como a mais flexível, pois permite o carregamento de literais de 5 *bits* em um ciclo de relógio ou literais de 16 *bits* em dois ciclo de relógio. Outra utilidade interessante desta instrução está montagem de valores de 32 *bits* no espaço reservado ao usuário, que se encontra nas primeiras posições da ROM, evitando que várias operações de aritmética, movimentação e memória sejam necessárias para realizar a mesma função.

sigo otimizações que são adotadas em boa parte das máquinas de pilha subsequentes. Teve relevante atuação no mercado como microcontrolador utilizado em impressoras, *switches* e aparelhos de telecomunicação em geral (PHILIP J. KOOPMAN, 1989).

#### 3.4 A CPU Mill

A CPU *Mill* é uma arquitetura de computadores de proposito geral onde a banco de registradores é organizada de forma circular e tamanho ajustável, utilizando-se de *Very Large Instruction Word* (VLIW) como paradigma de instrução. Sob o desenvolvimento de Ivan Godard e sua empresa chamada *Out Of The Box*, a máquina encontra-se em desenvolvimento no período em que este trabalho é escrito, porém, os desenvolvedores disponibilizam uma grande quantidade de informações a respeito do funcionamento da máquina (GODARD, 2015).

Como dito anteriormente, a máquina apresenta seu banco de registradores na forma circular. Com isto, cada processo a ser executado informa à máquina qual o tamanho da janela de registradores (*belt*) que necessita. Este *belt* se comporta como pilha circular, onde a última posição é sobrescrita pelo novo valor caso todas as posições do *belt* já esteja preenchida. Por se tratar de uma máquina de dois operandos, qualquer posição do *belt* pode ser acessada via instrução. Como o *belt* é circular o seu endereçamento é feito com base na última posição ao topo do *belt* que sofreu alteração, o índice de endereçamento dos registradores muda a cada inserção no *belt*, trazendo assim um paradigma de registrador temporal.

Este modelo de uso do banco de registradores encaixa-se no paradigma de pilha com dois operandos. Por um lado, não há a necessidade de renomeação pois os registradores são temporais, além de não haver dependência explicita entre registradores. Por outro, não há a necessidade de manipulações em pilhas para que os valores desejados se encontrem no topo, pois todas as posições são acessíveis.

Ao alocar um *belt* a máquina atribui a ele um identificador denominado *frame*, cuja a função é identificar o *belt* caso este seja guardado em memória e precise ser carregado novamente no futuro. Em outras máquinas de pilha mais complexas é comum encontrar o uso de *frames* para referenciar uma pilha a determinado processo, possibilitando assim uma troca de contexto organizada.

Quando há uma chamada de função, a instrução especifica quais valores serão usados como entrada para esta chamada. Estes valores são copiados na ordem em que se encontram no *belt* que executou a chamada (*caller*), para um novo *belt* que será da função que foi chamada (*callee*). Após isto, o *frame* contendo o *belt* do *caller* é guardado em memória e o *frame* do *callee* toma seu lugar. Após a computação, o *callee* chama o *frame* de seu *caller* e o carrega no *belt* da CPU, deixando carregados os valores de retorno como mostrado na Figura 11.

Figura 11: Manipulação dos *belts* ao chamar uma função.

Na alocação de um novo *belt*, além de especificar o tamanho que o *belt* terá, é atribuído a ele uma memória local de tamanho fixo chamada de *scratchpad*. *Scratchpad* é uma memória especial que se localiza na CPU, se assemelhando ao *belt*, porém é acessada como uma se fosse uma memória externa e é limpa assim que um *belt* é alocado. Seu comportamento é o de uma pilha, porém são necessários pelo menos três ciclos de relógio entre escrita e a leitura do mesmo valor no *scratchpad*.

O comportamento do *belt* é bem peculiar se comparado as demais máquinas de pilha analisadas neste Capítulo. O comportamento desta lembra um pouco uma máquina de pilha sem pilha de retorno, pois o *scratchpad* não se comporta como uma pilha de retorno mas sim como uma pilha de variáveis. Porém há uma alocação de um novo *belt* cada vez que uma função é chamada, diferindo-a bastante das demais implementações.

Por um lado as chamadas ficam mais organizadas pois somente os parâmetros são passados para o *belt* e só o retorno é adicionado ao *belt* do *caller*, se comparado a uma máquina de pilha

normal onde ambos *caller* e *callee* dividem a mesma pilha. Por outro lado, o uso extensivo de chamadas pode gerar uma grande quantidade de *frames* a serem guardados em memória, o que pode ser considerado sobrecarga. O tempo necessário para manipular todas as montagens e retornos de *frames* e seus *belts* pode ser muito custoso para o sistema em casos extremos de chamadas de função.

Embora a maioria das máquinas de pilha, especialmente as que rodam *Forth*, faça uso extensivo de chamadas de função, a CPU *Mill* foi pensada para a execução código *C*. Com isto, é seguro presumir que as chamadas de função não serão tão frequentes em um código *C*, como são em código *Forth*. A chamada de novos *belts* a cada *call* pode fazer sentido e vir a ser efetivo na execução de *C*.

É difícil fazer uma avaliação mais profunda da CPU *Mill* tendo em vista que o projeto esteja em desenvolvimento e nenhum tipo de *benchmark* ou demonstração esteja disponível. Os desenvolvedores afirmam que seu produto terá desempenho *2,3X* maior e menos consumo que uma máquina de registradores *superscalar* por quase a metade do preço. Tal *superscalar* não é especificada e tais afirmações não podem ser mais que estimativas, visto que o produto final não esta concluído. Resta esperar para que a primeira versão seja comercializada e avaliações de desempenho possam ser feitas, validando as afirmações dos desenvolvedores e a efetividade das otimizações.

## 3.5 Súmula

Após a análise dos principais aspectos de cada máquina abordadas neste capitulo, resta fazer uma comparação direta delas. A Tabela 8 mostra um apanhado das principais características de cada uma das máquinas analisadas, gerando uma comparação entre as abordagens adotadas em cada máquina.

Dentre as máquinas analisadas, todas as que implementam *Forth* apresentam uma CPU monociclo e uma pilha de dados, pilha esta que é um dos pré-requisitos para a linguagem. A CPU *Mill*, apesar de não ser explicitamente denominada de máquina de pilha pelos autores, tem em seu funcionamento básico o uso de estruturas de pilha em todas as suas estruturas de memória em CPU, classificando-a assim como uma máquina de pilha.

Tabela 8: Tabela comparativa entre as máquinas analisadas nesta capitulo.

|                            | J1         | Microcore                                                                    | Novix NC4016                                                  | Mill CPU   |

|----------------------------|------------|------------------------------------------------------------------------------|---------------------------------------------------------------|------------|

| Bits da arquitetura        | 16         | 8                                                                            | 16                                                            | 64         |

| Tamanho da pilha de dados  | 33         | Variável                                                                     | Variável                                                      | Variável   |

| Apresenta pilha de retorno | Sim        | Sim                                                                          | Sim                                                           | Não        |

| Alocação<br>das pilhas     | Local(CPU) | RAM                                                                          | Memória externa<br>dedicada                                   | Local(CPU) |

| Linguagem                  | Forth      | Forth                                                                        | Forth                                                         | С          |

| Número de operandos        | 0          | 0                                                                            | 0                                                             | >1         |

| Tipo de implementação      | VHDL       | VHDL                                                                         | ASIC                                                          | ASIC       |

| Aceita<br>modificações     | Não        | Módulos podem ser<br>adicionados e há<br>possibilidade de se<br>programar um | Bloco de memórias<br>externas dedicadas<br>podem ser trocados | Não        |

| Ciclos de execução         | Monociclo  | Monociclo                                                                    | Monociclo                                                     | Multiciclo |

Um ponto importante na escolha destas máquinas para a analise teórica é a alocação das pilhas usadas pela CPU. Na máquina *Microcore*, ambas as pilhas são alocadas em memória, o que traz flexibilidade à CPU pois as pilhas podem ser alocadas com tamanhos variáveis, além da vantagem das pilhas já se encontrarem escritas em memória em trocas de contexto.

Por outro lado tem-se a máquina *J1*, que aloca sua pilha em um banco de registradores. Com isto, esta máquina perde em flexibilidade comparada à máquina *Microcore*, pois suas pilhas tem um tamanho máximo fixo. Contudo, a forma de acesso às pilhas é mais rápido se comparado ao acesso à memória feito pela máquina *Microcore*.

Por fim a máquina *NOVIX NC4016* apresenta-se como uma máquina hibrida se comparada as maquinas citadas anteriormente, visto que esta usa de uma memória externa dedicada para a alocação de suas pilhas. Com isto, esta máquina consegue alcançar o mesmo grau de flexibilidade encontrado na alocação de pilhas em memória, contando ainda com um barramento otimizado para o acesso da memória externa pela CPU, diminuindo o tempo de acesso ao recurso.

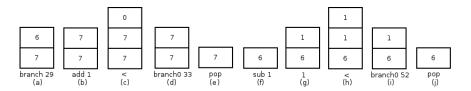

# 4 ANÁLISE TEÓRICA SOBRE AS MÁQUINAS DE PILHA

Neste capítulo, serão analisados os conceitos básicos sobre a forma de acesso e uso das pilhas, além da quantidade na CPU. A partir desta análise, serão propostas melhorias para cada uma destas análises, levantando quais as possíveis vantagens e desvantagens seriam encontradas nestas implementações.

# 4.1 Quantidade de pilhas

Conforme apresentado no Capítulo 2, a maior parte das máquinas de pilha são desenvolvidas para executar *Forth*. Este pode ser um dos fatores que contribuem para o reduzido interesse de pesquisa acadêmica e industrial sobre as arquiteturas do tipo pilha, citadas por ambos (BAILEY, 1996) e (PHILIP J. KOOPMAN, 1989). Além disto, a curva de aprendizado para a programação destas CPUs, especialmente no nível de programação encontrado em *Forth* que é muito similar à linguagem do *assembly* utilizado em máquinas de registradores.

# 4.1.1 Máquina de duas pilhas

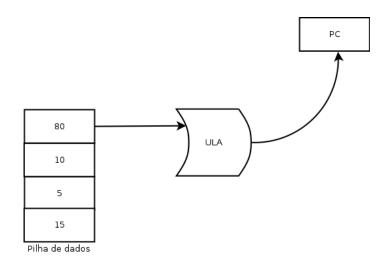

Apesar da forma de programação, a máquina base utilizada pela linguagem e pela máquina virtual *Forth* apresenta um conjunto de características interessantes. Para começar, o uso de duas pilhas, como visto no capitulo 2, facilita o controle do fluxo de dados e os separa do fluxo de endereços que é detido pela pilha de retorno. Para a implementação de máquinas *Forth*, a CPU enxerga e trata as pilhas como se fossem entidades de memória distintas uma da outra, mesmo estas sendo muitas vezes um mesmo bloco de registradores físico.

Esta característica é reforçada por instruções primitivas encontradas na linguagem *Forth* que explicitamente fazem transferência de dados entre as duas pilhas, como R@ (copia o topo da pilha de retorno para o topo da pilha de dados). Desta forma, a ULA terá de interagir quase que exclusivamente com a pilha de dados e somente em casos transferência entre pilhas a pilha de retorno será requisitada pela ULA.